# **INTERCHIP INTERCONNECTIONS**

### EKTA AGRAWAL & KUMAR MANU

Department of E & C Engineering, MIT, Moradabad, Uttar Pradesh, India

#### ABSTRACT

In this paper, the relatively fundamental work in the area of interconnections in digital computing systems is discussed. We cover comparisons of Carbon Nanotubes (CNTs) and optical interconnections in VLSI. The number of components per chip has grown and the cost decreasing dramatically. The copper interconnects can not fulfill different design requirements. There are many challenges for copper based interconnects. We are comparing carbon nanotubes interconnects and optical interconnects for global and semi- global wire interconnections. In this paper, we are comparing carbon nanotubes and optical interconnects in terms of latency and power dissipation.

KEYWORDS: Carbon Nanotubes, Interconnect, VLSI, Optical Interconnects

## **INTRODUCTION**

With continuous scaling of VLSI technology, coupling capacitance between interconnects lines need more accurate transmission line modeling, requiring the introduction of self and mutual inductances. Self and mutual inductances can cause for crosstalk noise and delay between high speeds VLSI interconnects. [1]. Carbon nanotube has excellent electrical properties like extra ordinary electrical conductivity, chemical processing and heat conductivity. Carbon Nanotubes used in manufacturing CNT based transistors, biomedical applications, energy storage etc. Optical interconnect becomes very popular and very important interconnects in digital computing. As, the demand of data, speed, reliability and high- performance is increasing, optical interconnects becomes the most suitable alternative for this purpose.

## **CARBON NANOTUBES (CNTS)**

One of the nano electronic architectures that have been reorganized as six emerging technologies for computers, known as Carbon Nano Tube (CNT)[2]. As, the resistivity of copper increases and current density demand increases to fulfill these requirements there was a requirement to identify new wiring solutions for deep nanometer scale VLSI technologies. Metallic carbon nanotubes (CNTs) are promising technology that can potentially accept the challenges faced by copper and thereby extend the lifetime of electrical interconnects [3].

Figure 1: Carbon Nanotubes

The copper interconnects cannot be committable with the IC interconnect requirements as the feature size continues to scale down to nanoscale. It is redicted that carbon nanotube (CNT) is superior than copper for VLSI interconnects in terms of conductivity, thermal management and reliability [4]. The performance of integrated circuits has

been growing exponentially, which has resulted in the development of a variety of VLSI products for communications, computers, and medical applications.

The **increase** in the performance is mainly due to the decrease in the dimensions of the integrated circuit chip. To sustain this improvement, the industry has to overcome several technological challenges in scaling the devices and interconnects. Metal interconnects have become a significant performance limiter. Carbon nanotubes could be as a possible replacement for copper as an interconnect material [5]. CNT field-effect transistors (CNTFETs) formed from individual single-walled nanotubes (SWCNTs), SWCNT bundles, or multi walled (MW) CNTs. The switching mechanism of CNT Field Effect Transistors shows that it involves the modulation by the gate field of Schottky barriers at the metal-CNT junctions. It is observed that subthreshold and vertical scaling behavior of CNTFETs, as well as their sensitivity to atmospheric oxygen is because of switching mechanism of CNT Field Effect Transistors [6]. Single-walled carbon nano tubes (SWNTs) have emerged as a very promising new class of electronic materials. Both metallic and semiconducting SWNTs are found to possess electrical characteristics that compare favorably to the best electronic materials available. Manufacturability issues, however, remain a major challenge [8]. The current-carrying capacity and reliability studies of multiwalled carbon nanotubes under high current densities (>109 A/cm2) show that no observable failure in the nanotube structure and no measurable change in the resistance are detected at temperatures up to  $250^{\circ}C$  and for time scales up to 2 weeks. Our results suggest that nanotubes are potential candidates as interconnects in future large-scale integrated nano electronic devices [9].

## **OPTICAL INTERCONNECTS**

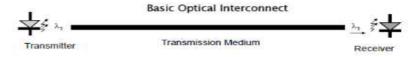

The increasing demand for bandwidth and interconnection density to provide wide bandwidth services at reasonably low cost are rapidly exhausting capabilities of interconnection techniques currently employed in conventional wide bandwidth telecommunication switching equipment. In particular, a bottleneck occurs at the intra-system (that is, board-, shelf- and cabinet-level) backplane interconnections. In order to address this problem, a variety of optical interconnection schemes have been proposed [10]. The advantages of optical interconnections in relation to the interconnection distance, the data capacity, and the interconnection functions are presented. The devices which will support practical implementation of optical interconnections and the integration of optical interconnection devices are discussed [11]. Optical Interconnects are highly applicable to parallel computing and for high throughput along with the compactness, and low latency over a long transmission medium. Optical interconnections will do much to alleviate transmission medium the communication limitations in the computer systems [12].

Interchips interconnections become more important for power efficient, high- bandwidth and low latency processor chips. It is shown by the studies that the bandwidth of traditional parallel interconnects with low I/O clock frequencies will become challenging problem in the future. Two types of high-bandwidth inter chip interconnects are developed to solve this problem. Low-swing differential electrical interconnects have been used in high-speed I/O designs and optical interconnects provide high bandwidth and low latency. Optical interconnects could improve the chip pin performance for many core processors. They are becoming alternatives for electrical interconnects. [13].

Figure 2: Fundamental of Optical Interconnect Network

Index Copernicus Value: 3.0 - Articles can be sent to editor.bestjournals@gmail.com

#### **Interchip Interconnections**

The optical link consists of an off- chip laser, a quantum- well modulator at the transmitter (converts CMOS gate output to optical signal), a waveguide comprising of a silicon core (refractive index  $\sim$ 3.5), a SiO<sub>2</sub> cladding as the transmission medium, and a trans impedance amplifier (TIA) followed by gain stages at the receiver. The total delay of an optical wire is the sum of the transmitter, waveguide, and receiver delays.

An on- chip optical link contains (a) A off chip Laser source which is coupled to the modulators; (b) Optical modulator that is used to manipulate a property of light often of an optical beam such as a laser beam; (c) an optical waveguide that can be implemented as a silicon strip waveguide or a rib waveguide for a 2- D confinement; (d) photodetector, generates current proportional to the incoming light intensity and (e) a trans impedance amplifier followed by gain stages [17].

Optical fiber communication is recognized as the cost-efficient and highest energy technique to offer ultra-large capacity for telecommunication networks. It has also been considered as a reliable transmission technology for data center applications. There is no feasible solution based on optical switching is available so far for handling the data center traffic at the edge tier. It is verified that the investigated passive optical interconnects can achieve a significant reduction of power consumption and maintain cost at a similar level compared to its electronic counterpart. Several research directions on passive optical interconnects have been pointed out for green data centers [14].

As data rates increase, optical interconnections at the boards and substrate levels become interesting alternatives for high performance interconnections according to Miller (2000) and Horowitz et al. (1998).Optical interconnection using embedded thin film photo detectors (PDs) in polymer waveguides is a chip to chip optical interconnection implementation that offers high speed interconnections with the potential for high integration density [15]. Optical interconnections have prospects for even better performance with improved devices and should facilitate the development of advanced digital systems, particularly if the technology can be made cost effective [16].

Optical data communication plays an important role in high speed data links. Especially in datacom applications data rates in Gbps area will be desired. An overall low cost approach is needed whether we uset the opto-electronic integration or the passive optical interconnects. Opto-electronic integration can be use through one- or bidirectional transceivers for datacom based on surface emitting lasers (VCSEL), instead of LEDs used now a days, and economically silicon detectors. The passive optical interconnects using beam shaped low-cost micro-optical components such as, microlenses for in- and out-coupling which are more popular in recently developed opto-electronical devices. [17].

## CONCLUSIONS

Electrical lines and connectors are replaced by free-space or guided-wave optics in high-speed, high-performance reliable digital systems. As clock rates reaches or exceed 1 GHz, optical transmission is best suitable medium for long distance communication. As the speed, functions per chip density increase, carbon nanotubes and optical interconnect are promising technology for interchip connections. On account of some bottlenecks of carbon nanotubes optical interconnects are the best option for interchip connections. There are several reasons for optical interconnects and carbon nanotubes to become an attractive alternative in parallel computing, digital systems, increasing demand of data and speed. Electrical interconnects are replacing by carbon nanotubes and optical interconnects.

#### REFERENCES

- Gupta, A.; Maheshwari, V.; Sharma, S.; Kar, R., "Crosstalk noise and delay analysis for high speed on-chip global RLC VLSI interconnects with mutual inductance using 90nm process technology," *Computing, Communication & Automation (ICCCA), 2015 International Conference on*, vol., no., pp.1215,1219, 15-16 May 2015

- Rezazadeh, M.; Safaei, F.; Moaiyeri, M.H., "Comparative Performance Study of Multi-stage Interconnection Networks Using Carbon Nanotube Switches," *Embedded and Ubiquitous Computing (EUC), 2011 IFIP 9th International Conference on*, vol., no., pp.326,331, 24-26 Oct. 2011

- 3. Banerjee, K.; Srivastava, N., "Are carbon nanotubes the future of VLSI interconnections?," *Design Automation Conference, 2006 43rd ACM/IEEE*, vol., no., pp.809,814, 0-0 0

- Yang Chai; Minghui Sun; Zhiyong Xiao; Yuan Li; Min Zhang; Chan, Philip C.H., "Towards future VLSI interconnects using aligned carbon nanotubes," in VLSI and System-on-Chip (VLSI-SoC), 2011 IEEE/IFIP 19th International Conference on, vol., no., pp.248-253, 3-5 Oct. 2011

- Thiruvenkatesan, C.; Raja, J., "Studies on the Application of Carbon Nanotube as Interconnects for Nanometric VLSI Circuits," in *Emerging Trends in Engineering and Technology (ICETET)*, 2009 2nd International Conference on , vol., no., pp.162-167, 16-18 Dec. 2009

- 6. Avouris, P.; Appenzeller, J.; Martel, Richard; Wind, S.J., "Carbon nanotube electronics," in *Proceedings of the IEEE*, vol.91, no.11, pp.1772-1784, Nov 2003

- Srivastava, N.; Joshi, R.V.; Banerjee, K., "Carbon nanotube interconnects: implications for performance, power dissipation and thermal management," in *Electron Devices Meeting*, 2005. *IEDM Technical Digest. IEEE International*, vol., no., pp.249-252, 5-5 Dec. 2005

- 8. McEuen, P.L.; Fuhrer, Michael S.; Park, H., "Single-walled carbon nanotube electronics," in *Nanotechnology, IEEE Transactions on*, vol.1, no.1, pp.78-85, Mar 2002

- Wei, B. Q., R. Vajtai, and P. M. Ajayan. "Reliability and current carrying capacity of carbon nanotubes." *Applied Physics Letters* 79.8 (2001): 1172-1174.

- Shahid, M.A.; Holland, W.R., "Flexible optical backplane interconnections," *Massively Parallel Processing Using* Optical Interconnections, 1996., Proceedings of the Third International Conference on , vol., no., pp.178,185, 27-29 Oct 1996

- 11. Wada, Osamu; Kamijoh, Takeshi; Nakamura, M., "Integrated optical interconnections," *Circuits and Devices Magazine, IEEE*, vol.8, no.6, pp.37,41, Nov. 1992

- 12. Nishimura, S.; Inoue, H.; Hanatani, S.; Matsuoka, H.; Yokota, T., "Optical interconnections for the massively parallel computer," *Photonics Technology Letters, IEEE*, vol.9, no.7, pp.1029,1031, July 1997

- 13. Wang, Zhehui, Jiang Xu, Peng Yang, Xuan Wang, Zhe Wang, Luan Huu Kinh Duong, Zhifei Wang, Rafael Kioji Vivas Maeda, and Haoran Li. "Improve Chip Pin Performance Using Optical Interconnects."

#### **Interchip Interconnections**

- 14. Chen, J.; Gong, Y.; Fiorani, M.; Aleksic, S., "Optical interconnects at the top of the rack for energy-efficient data centers," in *Communications Magazine, IEEE*, vol.53, no.8, pp.140-148, August 2015

- 15. Sang-Yeon Cho; Sang-Woo Seo; Jokerst, N.M.; Brooke, M., "Comparative high speed optical interconnections using thin film photodetectors embedded in polymer waveguides," *Electronic Components and Technology Conference, 2005. Proceedings. 55th*, vol., no., pp.1611,1616 Vol. 2, 31 May-3 June 2005

- 16. Tsang, D.Z., "Optical interconnections for digital systems," *Telesystems Conference*, 1992. NTC-92., National, vol., no., pp.9/1,9/6, 19-20 May 1992

- Frese, I.; Schwab, U.; Nahrstedt, E.; Klotzbucher, T.; Kunz, St.; Teubner, U.; Doll, T., "Polymer based optical interconnect module for a bidirectional transceiver and optical N/spl times/M star couplers for datacom applications with data rates > 1Gbps," in *Electronic Packaging Technology Conference, 2005. EPTC* 2005.Proceedings of 7th, vol.2, no., pp.6 pp.-, 7-9 Dec. 2005